SEGGER Evaluation Software for Cypress PSoC 5LP Development Kit

Downloads

SEGGER Evaluation Software

SEGGER Notifications

Subscribe to SEGGER Evaluation Software Notifications

Data Sheets

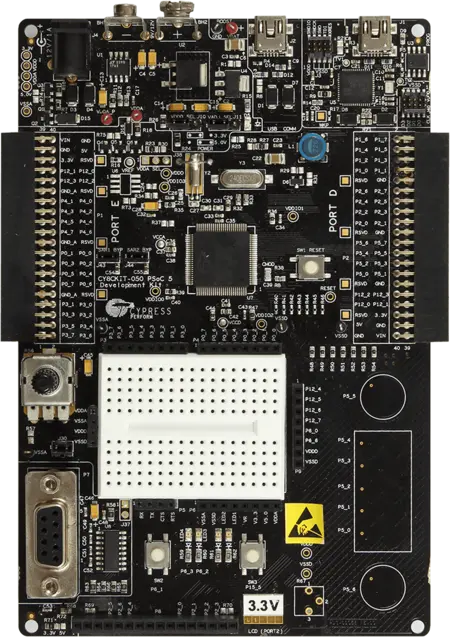

PSoC 5LP Development Kit

- Breadboard prototyping area

- 2 CapSense™ buttons and 5-element slider

- 4 user LEDs

- Power and status LEDs

- 2 user push-button switches

- Reset switch

- 2 expansion ports

- Potentiometer

- LCD header

- 24MHz and 32kHz crystals

- USB and UART interfaces

- Multiple power supply options: JTAG/SWD header, USB, boost converter, 9V battery, or external power

- 3.3V or 5.0V operation (jumper)

- JTAG/SWD debug connector 10 pin 0.1”

PSoC 5LP CY8C5868AXI-LP035

- 80MHz ARM Cortex-M3 CPU with single cycle multiply

- 256kB flash, 64kB SRAM, 2kB EEPROM

- 1kB of 4-way set-associative cache memory

- 24-channel direct memory access (DMA)

- CapSense® Touch Sensing with SmartSense™ Auto-Tuning

- 2 12-bit 1Msps sequenced SAR ADCs

- 20-bit 192ksps Delta-Sigma ADC

- 4 8-bit configurable IDAC/VDACs

- 4 opamps, 4 comparators

- 4 configurable multifunction analog blocks supporting PGA, TIA, Mixer and Sample&Hold

- High-precision 1.024V reference

- 4 16-bit Timer/Counter/PWM Blocks

- 4 PLD-based Logic Blocks (use for I2C, SPI, UART, etc.)

- Full CAN 2.0b with 16 RX, 8 TX buffers

- USB 2.0 using internal oscillator

- 24-bit fixed-point digital filter block (DFB) to implement FIR and IIR filters

- 72 I/Os (62 GPIO, 8 SIO, 2 USBIO) with flexible routing fabric

- LCD direct-drive from any GPIO

- Low power 0.50V to 5.50V operation

- 2µA Sleep mode, 300nA Hibernate mode