Overview

J-Link WiFi offers the same desirable features as J-Link BASE, and its wireless capabilities make it the debug probe of choice for use with target embedded devices that are stationary but moving or that have to be shielded from the surrounding environment. USB powered, J-Link WiFi can share a target device's power source, and it offers high-speed communication capabilities for supported target CPUs.

J-Link debug probes are supported by all major integrated development environments (IDEs), including Eclipse, GDB-based IDEs, and SEGGER's own Embedded Studio. A complete list of supported IDEs is available here. As the most popular debug probe for Arm and RISC-V cores, J-Link can safely be called the industry's de-facto standard.

Key features

High download speeds

J-Link WiFi offers download speeds of up to 1 MB/s, enabling project development that progresses smoothly and reliably, with minimized download times.

Real Time Transfer

J-Link WiFi offers SEGGER's Real Time Transfer (RTT) technology, which provides a simplified path for data transit when an application is running. In addition, changes in operation are easy to monitor.

Broad CPU and IDE support

J-Link WiFi works with an extensive range of microcontrollers and IDEs. It enables users to connect their selected microcontroller with their favorite IDE.

Supported devices

The list of supported manufacturers, families, devices, and systems on a chip includes tens of thousands of devices in hundreds of device families.

Device not listed? Please don’t hesitate to contact us.

Use cases

Mobility applications

For situations involving movement between the development PC and the target system, J-Link WiFi's debug interface can be used with the WLAN/WiFi interface. This is particularly useful in robotics applications.

Safety applications

For use cases involving a target system that operates within the confines of a hazardous environment, wireless connection enables a developer to keep the system outside of a dangerous area, even if there is a physical barrier between the development and target systems.

J-Link technology

Unlimited Breakpoints

Set as many breakpoints as you need in internal or external flash. Debug thoroughly, even when hardware breakpoints run out.

Monitor Mode

Keep essential system functions running while debugging. Perfect for real-time applications that must stay responsive.

RDI Support

Use standard RDI-compliant tools and IDEs with J-Link Pro. Access real-time code control, flash programming, and on-chip debug resources through a unified interface.

Power Profiling

Measure and optimize energy consumption with high sampling rates and 50 µA resolution. Ideal for battery-powered or energy-harvesting devices.

Tool set

J-Link WiFi comes with a versatile suite of software tools that enhance its performance and flexibility for debugging and programming. Utilities such as J-Link Commander, J-Link Configurator, and J-Link Remote Server make it a powerful and convenient tool for any development setup. Below are selected highlights from this tool set.

J-Link DSK

The J-Link Device Support Kit (DSK) allows silicon vendors and users to add debug and flash programming support for new devices. A new device typically requires a flash loader and, in some cases, a script defining special connect and reset sequences.

The DSK includes the SEGGER flash loader as well as a collection of example script files for devices that require special handling.

J-Link SDK

The J-Link Software Development Kit (SDK) enables the integration of J-Link and J-Trace support into custom applications. It is used in professional IDEs, such as SEGGER Embedded Studio, to enable direct debugging via J-Link / J-Trace, as well as in customized production utilities. Available for Windows, Linux, and macOS, the SDK can be used with nearly any programming language or solution.

Software

As a multi-platform solution, J-Link WiFi comes with setup and control software for Linux, macOS, and Windows. Software and firmware updates are included, and all software is included free of charge. The J-Link Software and Documentation Package is available here:

Customer support

J-Link WiFi comes with one year (12 months) of Basic Support. Beyond that, SEGGER's Extended Coverage gives users the option to extend the hardware warranty and Basic Support for one additional year (12 months) or two additional years (24 months). These options are only available at the time of purchase, either through the Web Shop or upon request; adding coverage at a later date is not possible.

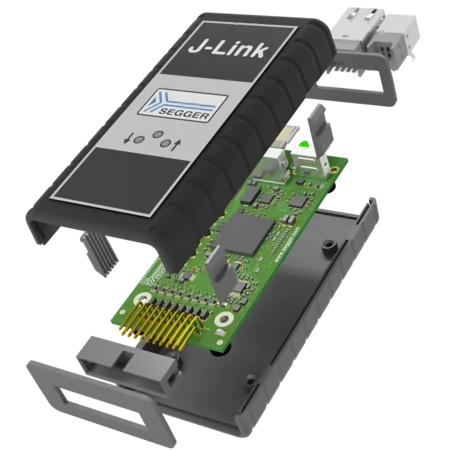

Product images

Technical specifications

| Specification | Value |

|---|---|

| Supported OS | Microsoft Windows (x86 / x64 / Arm64), Linux (x86 / x64 / Arm / Arm64), macOS (x64 / Apple Silicon) |

| Electromagnetic compatibility (EMC) | EN 301 489-1/-17, EN 300 328, EN 62368 |

| Operating temperature | +5°C ... +60°C |

| Storage temperature | -20°C ... +65 °C |

| Relative humidity (non-condensing) | Max. 90% rH |

| Mechanical | |

| Size (without cables) | 103mm x 53mm x 28mm |

| Weight (without cables) | 70g |

| Available Interfaces | |

| WiFi interface | IEEE 802.11 b/g/n (2.4 GHz) |

| USB interface | USB 2.0 (Hi-Speed) |

| Target interface | JTAG / SWD 20-pin |

| JTAG/SWD Interface, Electrical | |

| Power supply | USB powered, max. 220mA@5V |

| Target interface voltage (VIF) | 1.2V ... 5V |

| Current drawn from target voltage sense pin (VTRef) | < 25µA |

| Target supply voltage | 5V (derived from USB voltage) |

| Target supply current | Max. 300mA |

| Reset type | Open drain with 100 Ohms series resistor. Can be pulled low or tristated |

| Reset low level output voltage (VOL) | VOL <= 10% of VIF |

| For the whole target voltage range (1.2V <= VIF <= 5V) | |

| LOW level input voltage (VIL) | VIL <= 40% of VIF |

| HIGH level input voltage (VIH) | VIH >= 60% of VIF |

| For 1.2V >= VIF <= 3.6V | |

| LOW level output voltage (VOL) with a load of 10 kOhm | VOL <= 20% of VIF |

| HIGH level output voltage (VOH) with a load of 10 kOhm | VOH >= 80% of VIF |

| For 3.6 <= VIF <= 5V | |

| LOW level output voltage (VOL) with a load of 10 kOhm | VOL <= 20% of VIF |

| HIGH level output voltage (VOH) with a load of 10 kOhm | VOH >= 80% of VIF |

| JTAG/SWD Interface, Timing | |

| Target interface speed | Max. 15 MHz |

| SWO sampling frequency | Max. 30 MHz |

| Data input rise time (Trdi) | Tfdi <= 20ns |

| Data output rise time (Trdo) | Trdo <= 10ns |

| Data output fall time (Tfdo) | Tfdo <= 10ns |

| Clock rise time (Trc) | Trc <= 3ns |

| Clock fall time (Tfc) | Trc <= 3ns |

Latest news

Get in touch with us

Have questions or need assistance? Our Embedded Experts are here to help!

Reach out to us for:

- Licensing quotes

- Technical inquiries

- Project support